欸,最近大家都在聊的AI伺服器,背後有個超重要的技術你們知道嗎?

哈囉各位~最近不論是NVIDIA還是台積電,大家都在喊一個酷東西叫CPO (Co-Packaged Optics),中文翻作「共同封裝光學」。 簡單講,就是把處理訊號的晶片(ASIC)和負責光傳輸的矽光子晶片(PIC)包在同一顆IC裡面。 這樣做的好處是能讓訊號傳得更快、功耗更低,根本是為了解決AI巨量資料傳輸的塞車問題而生的。👍

不過呢,把電子跟光學元件塞在一起,雖然聽起來很美好,但在生產線上可是個大挑戰。特別是在「晶圓測試」這個階段,也就是晶片還沒被切下來、還是一整片圓圓的晶圓時就要先檢查它是不是好的。 這一步沒做好,後面都是白搭,等於是把有問題的晶片包進昂貴的封裝裡,成本直接爆炸。 所以今天就來跟大家聊聊,這個光電整合元件的晶圓測試,到底是在測什麼,又有哪些好玩的地方。

一句話結論

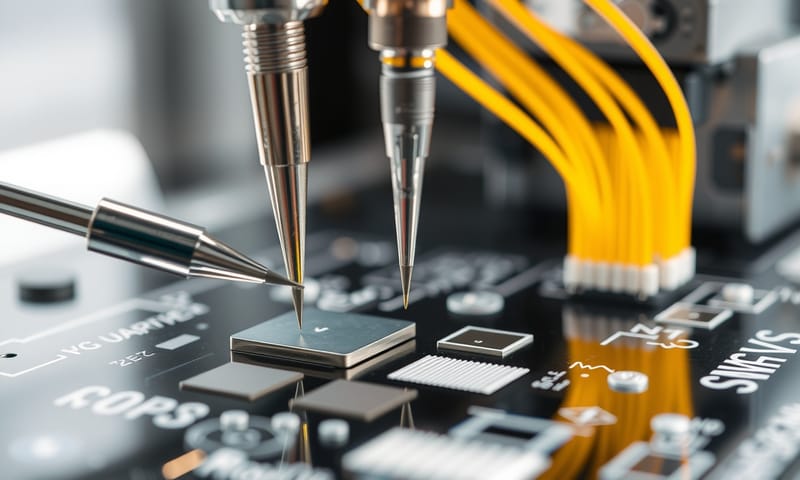

簡單來說,光電整合晶片的晶圓測試,就是除了要測「電」的特性,還必須同時搞定「光」的測試,等於是要在一個超級小的晶片上,同時插上電的探針和光的探針(光纖),技術難度直接三級跳。😂

為什麼光電晶片的測試這麼麻煩?

大家可以想像一下,傳統的晶圓測試,就像拿著很細的探針去戳晶片上的金屬點,看看電通不通、訊號對不對。 這已經很難了,因為那些點都超級小。但現在矽光子的晶片,你不只要用電的探針,還要拿一根或一排「光纖」去對準晶片上比頭髮還細的「光波導」,把光打進去,然後在另一端用另一根光纖把光接出來,測量光的損耗、頻寬等等。 這整個過程超級搞剛,主要有幾個大魔王:

- 對位對到天荒地老:光纖跟晶片上的光柵耦合器(Grating Coupler)對位,要求是奈米等級的精準度。 只要稍微偏一點點,光的損耗就會急遽增加,測出來的數據就不準了。 所以測試機台必須要有超高精度的六軸定位平台,才能重複又快速地完成對位。

- 光跟電的戰爭:有時候,電的探針卡 (Probe Card) 會擋到光纖的路,或是光纖陣列 (Fiber Array) 會跟電探針打架。 尤其是在需要同時測高頻電訊號跟光訊號的時候,兩邊的擺放位置、散熱問題,都要想辦法解決,這對探針卡和整個測試系統的設計是一大考驗。

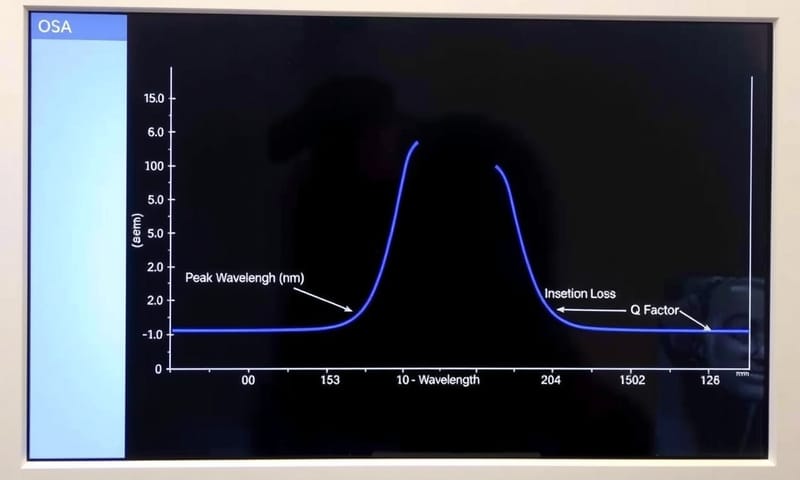

- 測試項目五花八門:不只要測電的參數(像電阻、電容),還要測一堆光的參數,例如插入損耗 (Insertion Loss)、偏振相關損耗 (PDL)、眼圖 (Eye Diagram)、誤碼率 (BER) 等等。 這代表測試機台需要整合可調式雷射、光功率計、光譜分析儀、誤碼儀等一堆昂貴的光學儀器。

我自己是覺得,這也說明了為什麼現在全球那幾家大的測試設備商,像是美國的Keysight、VIAVI Solutions,還有台灣的旺矽、穎崴,都在卯足全力開發新的解決方案。 因為誰能先把這個又快又準又穩的「光電同測」方案搞定,誰就能在下一代的AI硬體市場搶到先機。

所以,實際的測試流程長怎樣?

好啦,說了這麼多挑戰,那實際在產線上,到底是怎麼一步一步做的?雖然每家公司細節可能不同,但大致上可以分成幾個步驟:

- 晶圓載入與校準:首先,機器手臂會把一片佈滿數千個晶片的晶圓,放到測試機台(Prober)的載盤(Chuck)上。 接著,用攝影機做影像辨識,精準定位晶圓的中心和方向。

- 電性預檢 (DC Test):通常會先用電的探針卡,對晶片上的一些基本電路進行直流測試,像是檢查有沒有短路或斷路。 這一關沒過的,後面貴桑桑的光學測試就不用做了,直接標記為不良品 (Fail die)。

- 光纖對位 (Fiber Alignment):這就是最關鍵也最花時間的一步。 測試系統會控制探針頭上的光纖陣列,移動到第一個要測的晶片上方。然後,系統會啟動一個「搜尋演算法」,一邊發射光,一邊微調光纖在X、Y、Z三個方向甚至角度上的位置,直到接收端的功率計收到最大的光功率為止。 這整個過程必須在幾秒內完成。

- 光學特性量測 (Optical Test):對準之後,重頭戲就來了!測試系統會控制各種儀器,開始進行一系列的量測。例如,用可調式雷射掃描不同的波長,測量每個波長下的光損耗,這就是看晶片內部的光路順不順。 或是給它一個高速的電訊號,看看它轉出來的光訊號品質好不好(這就是E/O測試)。

- 數據記錄與換下一顆:測完一顆晶片的所有參數後,系統會把結果存成一個叫做Wafer Map的檔案,在地圖上標示這顆晶片是好(Pass)是壞(Fail)。 然後,載盤會快速移動到下一個晶片,重複步驟3到5,直到整片晶圓上的所有晶片都測完為止。

- 晶圓出站:整片測完後,機器手臂會把晶圓取出,送到下一站(通常是切割站),準備把那些被標記為「Pass」的好晶片切下來,進行後續的封裝。

跟傳統純電晶圓測試差在哪?一張表看懂

為了讓大家更有感覺,我弄了個簡單的比較表。你可以看到,多了「光」之後,所有事情都變得複雜很多。😂

| 項目 | 傳統純電晶圓測試 (Electrical-Only) | 光電整合晶圓測試 (Electro-Optical) |

|---|---|---|

| 測試介面 | 就只有探針卡 (Probe Card),相對單純。 | 除了探針卡,還要加上光纖陣列 (Fiber Array)。兩邊要怎麼擺才不會打架,就是個大學問。 |

| 對位技術 | 二維平面 (X-Y) 對準探針跟金屬墊 (Pad) 就好,通常是微米等級。 | 六軸立體 (X, Y, Z, Pitch, Yaw, Roll) 對準,而且光纖跟波導的間距和角度都要抓到奈米級,超麻煩! |

| 關鍵儀器 | 電源供應器、數位三用電錶、示波器… 主要都是電子量測儀器。 | 除了電的儀器,還要加上可調式雷射、光功率計、光譜分析儀、偏振控制器… 整套都是錢。🤑 |

| 測試挑戰 | 主要是高頻訊號的完整性、探針的接觸電阻、還有針的壽命。 | 光耦合效率低、對位時間長、偏振敏感性、溫度影響光學特性… 每個都是魔王關卡。 |

| 產業玩家 | 很多成熟的廠商,技術相對標準化。 | 門檻超高,目前是FormFactor、Technoprobe、旺矽、穎崴這些廠商在主導。 台灣廠商在這塊其實很強! |

未來趨勢:測試也要跟著AI一起進化

隨著AI晶片對頻寬的要求越來越高,CPO技術肯定會越來越普及。 這也代表晶圓測試技術必須跟上腳步。我觀察到幾個趨勢:

- 更快的自動化對位:現在花在對位的時間還是佔了測試很大一部分成本。 未來絕對會看到更多利用機器學習或AI演算法,來優化光纖搜尋路徑、縮短對位時間的技術。

- 測試左移 (Shift-Left):與其等到最後封裝完才發現問題,不如在更早的晶圓階段,就做更多「功能性測試」,而不只是測基本參數。 比如說,直接在晶圓上模擬高速傳輸訊號,看誤碼率表現,提早篩選出體質好的晶片。

- 異質整合的挑戰:未來的CPO可能會直接把雷射光源也整合到晶片上(目前大多是外接雷射)。 這會帶來新的散熱和測試挑戰,因為雷射對溫度非常敏感,測試時的溫控要做得更精準。

說到這個,就很有趣了。美國的標準或是一些國際大廠像Keysight、Viavi會比較強調從元件物理特性出發的參數測試。 但在台灣,因為我們有像台積電、日月光這樣強大的製造和封測生態系,所以會更早看到像穎崴、旺矽這些廠商,直接推出整合度很高的「系統級」測試方案,去滿足客戶量產的需求。 這種務實、快速解決產線問題的風格,真的是台灣廠商的強項。

總之,光電整合元件的晶圓測試是一個正在快速發展、而且挑戰跟機會都超級多的領域。它不像晶片設計或製程那樣光鮮亮麗,但卻是決定AI硬體能不能順利量產、降低成本的無名英雄。下次當你看到那些超強的AI伺服器時,可以想想背後有這麼一群工程師,正在為了如何又快又準地幫晶片「點光明燈」而奮鬥著呢!😂

今天就先聊到這~大家對於這種光電整合的測試有什麼想法嗎?或是你覺得在AI時代,還有哪些不起眼但超重要的技術?歡迎在下面留言分享喔!