先說結論:晶圓級測試,問題都在光路對準跟錢

好,長話短說。把 SiPh 的測試從封裝後拉到晶圓階段,最大的目的就是省錢。你想想看,一顆有問題的晶片,你還花錢去封裝它,最後才發現是壞的,這不是很虧嗎?所以大家就想在切片之前,在整片晶圓上就把壞的挑出來,這就叫晶圓級測試 [wafer-level test]。 可是吼,這件事的魔鬼細節,說穿了就兩件:第一,你的光要怎麼「插」進去跟「抽」出來,那個對準的精準度要求是奈米等級的;第二,就是整套設備非常、非常貴,而且測試速度跟量產要求的吞吐量 [throughput] 常常是對不上的。

所以,如果你正在評估要不要導入或升級 SiPh 的晶圓級測試,我會說,你先不要只看那些設備商型錄上寫的規格,你要先搞清楚你自己的產品,它的光學接口是哪一種?是光柵耦合器 [Grating Coupler] 還是邊緣耦合 [Edge Coupler]? 這會直接決定你需要什麼樣的探針台跟光纖陣列 [Fiber Array]。 然後,再去思考你的測試是為了研發?還是真的要上線量產?這兩者的設備選型邏輯,老實說,完全是兩回事。

網路上都有講,但沒說清楚的那些事

OK,我稍微查了一下,網路上大部分的資料,不管是技術文章還是廠商的白皮書,都會提到幾個挑戰。 他們會說,啊,光耦合很難啦,要六軸定位啦,要考慮偏振啦,還有高速訊號的量測什麼的。 這些都對,但我覺得他們沒有把那個「痛」講得很具體。

比方說,他們會說光纖跟晶圓上的波導 [waveguide] 尺寸差很多,所以需要特殊結構來對準。 沒錯,但真正的問題是,這個對準的過程超級花時間,而且很容易因為一點點震動或溫度變化就跑掉。 在實驗室裡手動調半天,可能可以得到一個漂亮的數據,但搬到產線上,要求每小時測幾百幾千個點,那個自動化對位的演算法跟硬體穩定性,才是真正值錢的地方。

另外一點是,很多文章只談光學參數,像是插入損耗 [Insertion Loss, IL] 或偏振相關損耗 [Polarization Dependent Loss, PDL]。 但 SiPh 晶片是「光電整合」的,上面還有調變器 [modulator] 跟偵測器 [detector] 這些需要吃電、送電的元件。 所以你其實需要「光」跟「電」的探針同時下針,這就變成一個很複雜的機構問題。電的探針卡 [probe card] 跟光纖探針要怎麼在小小的空間裡共存,還不能互相干擾,這才是選設備的時候要看的眉角。

最近甚至有台灣的廠商,像是光焱科技,開發出了新的技術,可以直接在晶圓上掃描光損耗的「熱點」,把抽象的損耗數字變成可視化的影像,這就比傳統只給你一個 IL 數字的黑箱測試要有用多了。 這種新技術的出現,代表大家已經不滿足於「測過」,而是要「知道錯在哪」。

所以,到底要怎麼測?關鍵步驟拆解

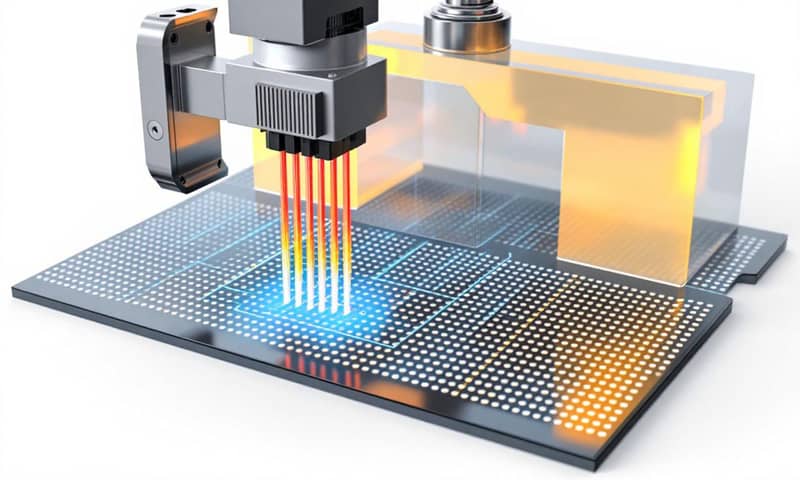

好,那我們來講實際的。一套完整的 SiPh 晶圓級測試系統,大概是長這樣:你需要一個超穩的探針台 [Probe Station],上面架著高精度的多軸位移平台。 然後,你需要用光纖陣列 [Fiber Array Unit, FAU] 把光送進晶片,再從另一端接收出來。 光源通常是可調式雷射 [Tunable Laser],接收端是光功率計 [Optical Power Meter]。 如果要測高速元件,那還得加上網路分析儀、示波器這些射頻儀器。

整個流程的核心挑戰,就是「光纖對準」。這一步沒做好,後面測什麼都不準。

主要有幾個關鍵點:

- 耦合方式的選擇:你的晶片是用光柵耦合器還是邊緣耦合?光柵是在晶片表面,光從「垂直」或帶一個小角度的方向進出,所以光纖探針是從上方下去;邊緣耦合則是在晶片切開後的側面,光是「水平」進出的。 這兩種方式對應的探針台結構完全不同。

- 主動對準與盲搜:你不可能用肉眼去對。系統必須具備自動化的「盲搜」功能,就是讓光纖在一個範圍內移動,同時監測光功率,找到訊號最強的那個點,然後鎖定。 這個搜尋演算法的速度和準確性,直接影響你的測試效率。

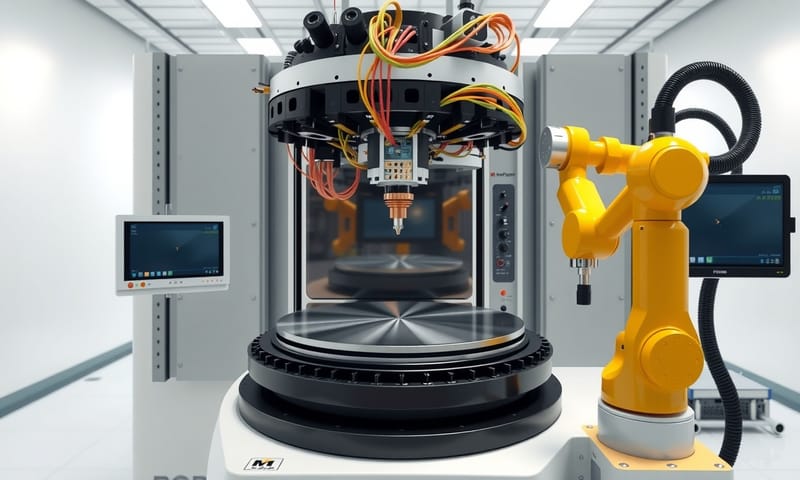

- 光電混合測試:當你需要同時測量光學和電學特性時,例如測一個調變器的眼圖 [eye diagram],你就必須讓 RF 探針跟光纖探針同時接觸到待測物 [DUT]。這時候,探針卡的設計就很重要,要怎麼避開光路,又要確保高頻訊號的完整性,這都是學問。台灣的穎崴科技就有針對 CPO 推出這種整合探針卡、測試座和溫控的方案。

- 偏振控制:矽波導對光的偏振方向很敏感,所以有時候你需要在光路中加入偏振控制器,去測量在不同偏振狀態下的元件性能,也就是 PDL。

設備選型:實驗室玩票 vs. 產線印鈔

聊到設備選型,這真的要看你的目的是什麼。我把它簡單分成兩種情境:一種是研發階段,在實驗室裡用的;另一種是真正要上產線,追求產能跟良率的。

底下我做了一個簡單的比較表,讓你感受一下那個思維上的差異。

| 考量點 | 研發/實驗室等級設備 | 量產等級設備 |

|---|---|---|

| 核心目標 | 功能驗證、特性分析。搞懂元件為什麼好、為什麼壞。彈性最重要。 | 吞吐量!吞吐量!吞吐量! 就是要在最短時間內,把壞的晶片篩出來。穩定性和速度壓倒一切。 |

| 自動化程度 | 半自動就可以了。很多參數可能需要工程師手動調整、探索。 有時候用手動平台慢慢調,反而能發現問題。 | 必須是全自動。 從晶圓載入、mapping、對位、測試、到數據上傳,最好都不要有人工干預。最好還要支援 SECS/GEM 通訊協定。 |

| 光學對位 | -精度要高,但速度可以慢一點。通常會有很多時間讓你去 fine-tune 那個六軸平台。 | -速度要快,而且要「一次到位」。通常會有很強大的演算法,用來做快速的峰值搜尋 [peak search]。 | -

| 軟體與整合 | -軟體功能要強大,方便做各種參數掃描、數據分析。可能由好幾個不同廠商的儀器(雷射、功率計、示波器)拼起來。 | -軟體要跟工廠的 MES 系統整合。重點是測試流程的穩定執行和數據的自動記錄。通常會是像 FormFactor 或 Keysight 這種大廠提供的整合方案。 | -

| 成本考量 | -幾百萬台幣可能搞得定一個基本平台。可以慢慢添購周邊儀器。 | -呃... 幾千萬甚至上億台幣都是有可能的。這是一筆巨大的資本支出。 | -

你看,思維完全不同吧?所以不要拿著研發的需求去買量產的設備,那會浪費很多錢;反過來,拿實驗室的拼裝車想去跑量產,那你的產線良率跟效率會是一場災難。

現實的骨感:標準不一與在地化挑戰

最後,我想提一下更現實的問題。SiPh 這個領域,特別是測試,其實還很新,很多東西沒有統一的標準。 比如說,大家對於測試 Pad 的 layout design rule 就沒有共識。 有些人習慣把光學 I/O 放東、西兩側,電學的放南、北兩側,但這不是強制規定。

這就導致一個問題,你從 A 晶圓廠拿到的片子,跟 B 晶圓廠的,可能需要完全不同的探針卡和測試程式。這對設備整合來說很頭痛。

再來就是「在地化」的差異。國外像 Keysight、FormFactor 這些大廠,他們提供了非常強大且完整的解決方案。 他們跟國際上一些大的研究單位,像是比利時的 IMEC,有很深的合作,定義了很多前沿的測試方法。 但這些方案通常非常昂貴,而且維護保養的成本也高。

反觀台灣,我們有非常強的半導體製造聚落。所以也出現了一些在地的測試方案供應商,像是前面提到的穎崴、旺矽,還有一些系統整合商。他們的優勢在於離客戶很近,服務即時,而且價格可能更有彈性。例如,工研院早期就和 Keysight、FormFactor 合作建立了測試平台,把這些技術引進台灣,然後本地廠商再根據客戶需求去做客製化和優化。台灣的采鈺科技也提供晶圓級的測試服務,讓客戶在晶圓階段就能取得數據,節省成本。

所以,我的建議是,如果你是大型的一線廠,不缺預算,直接找國際大廠的 turn-key solution 可能是最穩的。但如果你是新創公司,或者你的產品比較特殊,不妨多跟台灣在地的廠商聊聊,他們或許更能理解你的痛點,並提供客製化的服務。

總之,SiPh 的晶圓級測試是一個正在快速發展的領域。它很複雜,也很昂貴,但這是邁向 CPO 和更高速光通訊時代的必經之路。 選對工具、用對方法,才能在這場競賽中活下來。

最後想問一下正在看這篇的各位,如果你的團隊也在做 SiPh 相關的產品,目前在測試這關,你覺得最大的瓶頸是什麼?是初期設備的資本投入太高?是測試程式開發太花時間?還是量產的吞吐量一直上不來?在下面留言分享一下你的看法吧!